# INSTRUCTION MANUAL

## DIGITAL DELAY LINE MODEL 1745M

## LIMITED WARRANTY

THE EVENTIDE MODEL 1745M DIGITAL DELAY IS WARRANTED FOR A PERIOD OF 1 YEAR

from the date of purchase from Eventide or an authorized dealer, against defects in material or workmanship. In case of difficulty, contact Eventide or your dealer for instructions.

This warranty does not apply to mechanical defects caused by use or rough handling, or to damage caused by improper operation not in accordance with this manual. Cause of defect is in the sole judgment of Eventide.

Much of the circuitry in the DDL is manufactured with static sensitive MOS and CMOS components. If you are requested to return a defective circuit card, this card MUST be wrapped in aluminum or other conductive foil. If this is not done, the warranty for the card in question is void.

The warranty is voidable at Eventide's option under the following circumstances: user makes unauthorized modifications of any type; or, the unit is connected to an improper voltage supply.

If the unit is modified by the customer without permission, the customer agrees to pay for any time or parts necessary to remove the modification before repair.

Eventide will under no circumstances be responsible for consequential damages caused by failure of equipments of its manufacture, or for any other reason. Our sole liability is for repair or replacement of the defective equipment under the terms of the warranty.

#### SHIPPING

Equipment should be returned, if possible, in the original packing container. Loose cards should be wrapped in conductive foil. If the original container is not available, the equipment should be packed to prevent damage from crushing and dropping. We recommend UPS over US mail, and air freight if you're in a hurry. If, in our opinion, the packing container is improper for return shipping, we reserve the right to supply a new container and charge for same.

The warranty covers return shipping by UPS within the continental US except Alaska. Return shipments will not be insured unless customer requests and agrees to pay for same. If a more expensive method of shipment is requested, the customer will be charged for the difference.

Foreign shipments must be returned fully prepaid, including customs and brokerage charges. Repaired equipment will be shipped all charges collect.

## EVENTIDE CLOCK WORKS INC.

| WARRANTY | REGISTRATION | FORM |

|----------|--------------|------|

|----------|--------------|------|

-

-

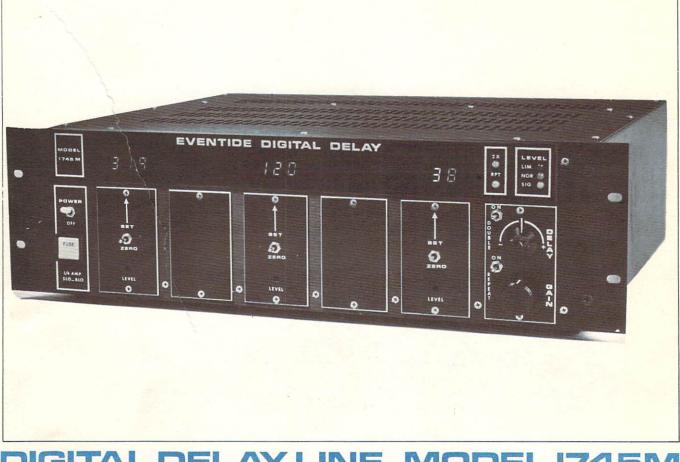

DIGITAL DELAY LINE 1745M

| RIAL NUMBERDATE PURCHASED                                                                                           |                                     |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|

| FROM WHOM PURCHASED                                                                                                 |                                     |  |  |  |

|                                                                                                                     |                                     |  |  |  |

| NAME OF PURCHASER                                                                                                   |                                     |  |  |  |

| ADDRESS                                                                                                             |                                     |  |  |  |

| CITY                                                                                                                | STATEZIPTEL                         |  |  |  |

| CONFIGURATIONOUTPUTS                                                                                                | TRANSFORMERSVOLTAGE                 |  |  |  |

| OTHER                                                                                                               |                                     |  |  |  |

| THE 1745M is an expandable system and we wo<br>they become available. To whom should this<br>NAME<br>               | information be sent?                |  |  |  |

|                                                                                                                     |                                     |  |  |  |

|                                                                                                                     |                                     |  |  |  |

| OPTIONAL-PLEASE FILL OUT IF YOU HAVE TIME                                                                           |                                     |  |  |  |

| NATURE OF YOUR BUSINESS                                                                                             |                                     |  |  |  |

| APPLICATION FOR THE DDL. IF SOUND REINFORCEMENT, ADDRESS OF SITE                                                    |                                     |  |  |  |

| · · ·                                                                                                               |                                     |  |  |  |

|                                                                                                                     |                                     |  |  |  |

| <b>`</b>                                                                                                            |                                     |  |  |  |

| HOW DID YOU LEARN ABOUT EVENTIDE EQUIPMENT?                                                                         |                                     |  |  |  |

|                                                                                                                     |                                     |  |  |  |

| IMPORTANT: YOU MUST FILL OUT THIS F<br>A BUSINESS REPLY ENVELOPE IS PROVIDE<br>BE MAILED WITHIN 10 DAYS OF PURCHASE | D FOR YOUR CONVENIENCE. FORM SHOULD |  |  |  |

## TABLE OF CONTENTS

Ľ

Ľ

L

Ľ

Ľ

Ľ

Ľ

Ľ

Ľ

Ľ

| Warranty<br>Warranty Registration Form<br>Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                   | i<br>ii<br>iv                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| OPERATING MANUAL:                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| What to Do if You Can't Wait!<br>Instruction Manual Manual<br>Specifications<br>Interconnection<br>Control and Indicator Description<br>Input Level Settings<br>Delay Doubling<br>Article: The Digital Delay Line Revisited<br>Applications<br>Article reprint: Phasing and Flanging<br>More Applications<br>TECHNICAL INFORMATION:                                                                                                                           | 1<br>2<br>3<br>4<br>5<br>7<br>9<br>10<br>17<br>19<br>22                          |

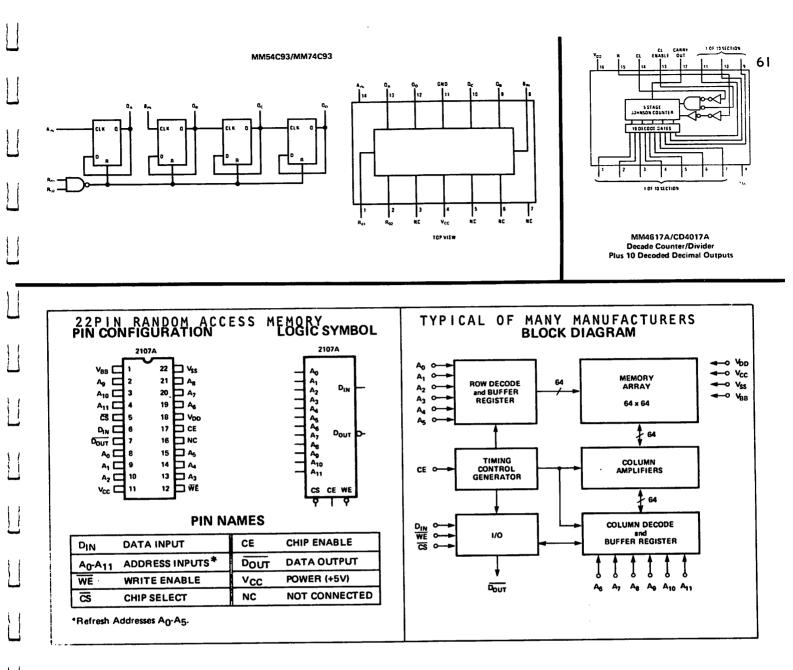

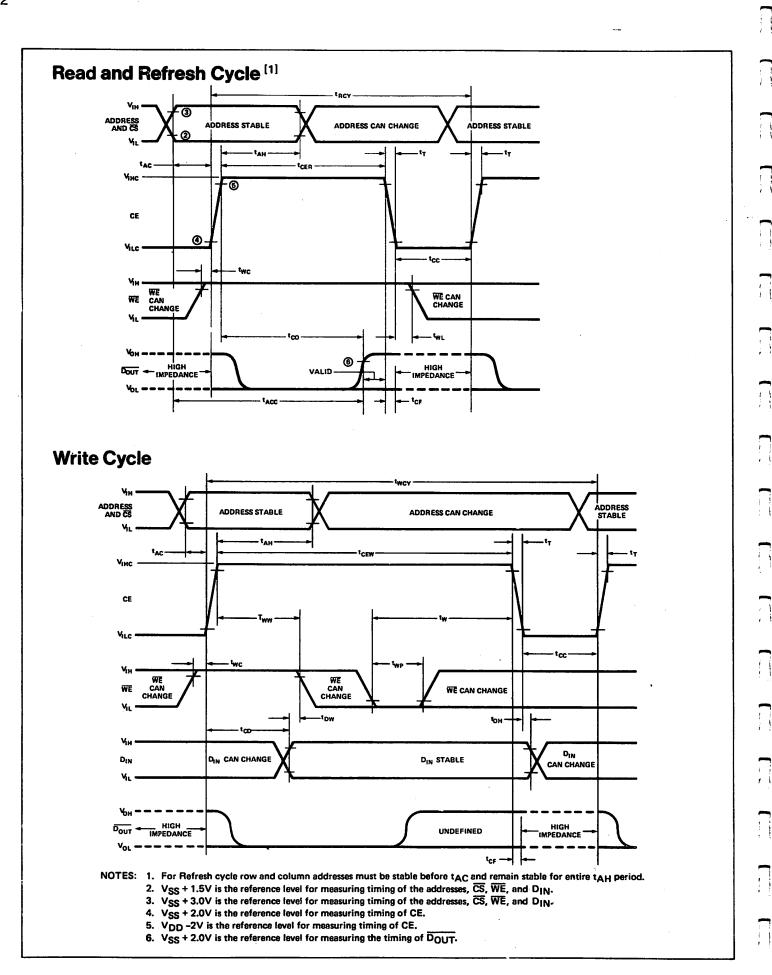

|                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95                                                                               |

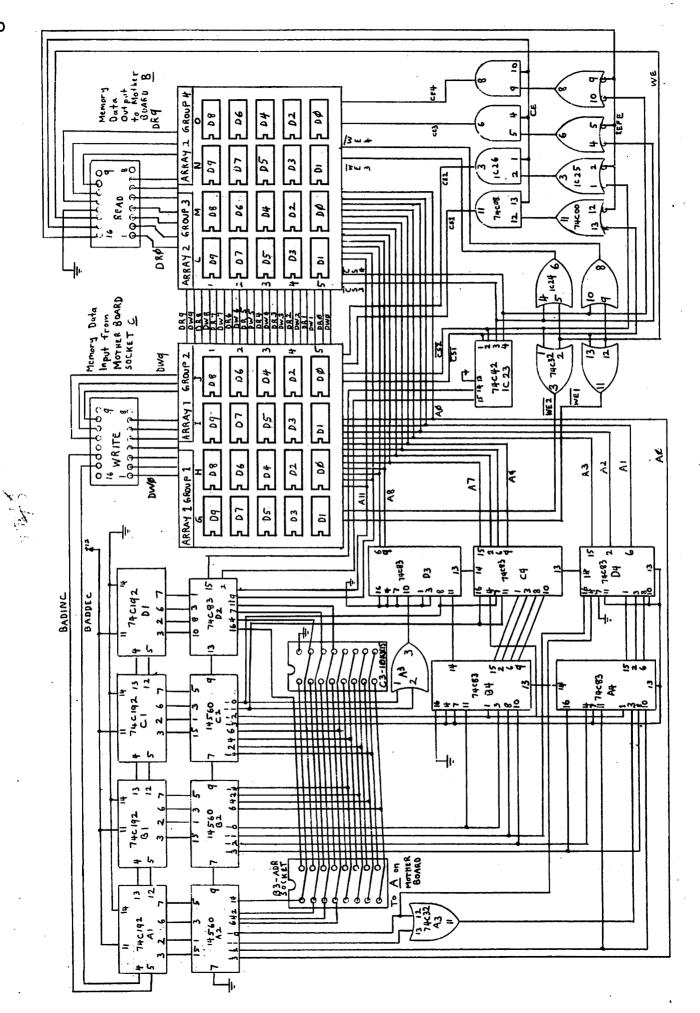

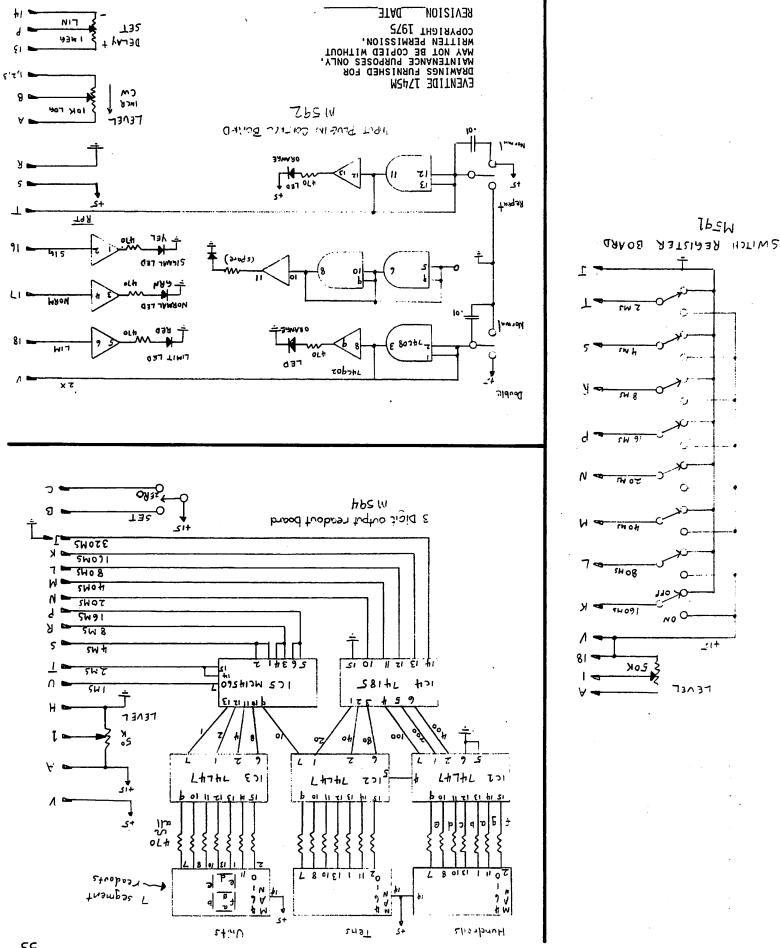

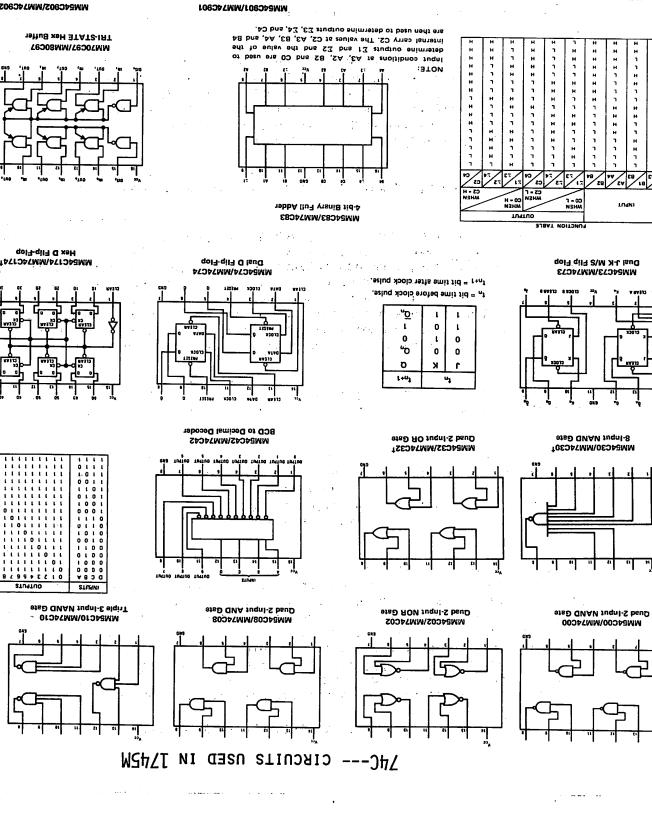

| Introduction<br>Test Equipment Required<br>Performance Assurance<br>Troubleshooting<br>Trouble indications<br>Alignment Instructions<br>Theory of Operation<br>Mother board<br>Random Access Memory Board<br>Input Filter and Timing Board<br>Input Filter and Timing Board<br>Output D/A and Control Register Board<br>Output D/A and Control Register Board<br>Output Board Readout Assembly<br>Mechanical Assembly and Access<br>Adding Additional Outputs | 25<br>26<br>27<br>29<br>30<br>32<br>33<br>33<br>35<br>38<br>38<br>39<br>41<br>42 |

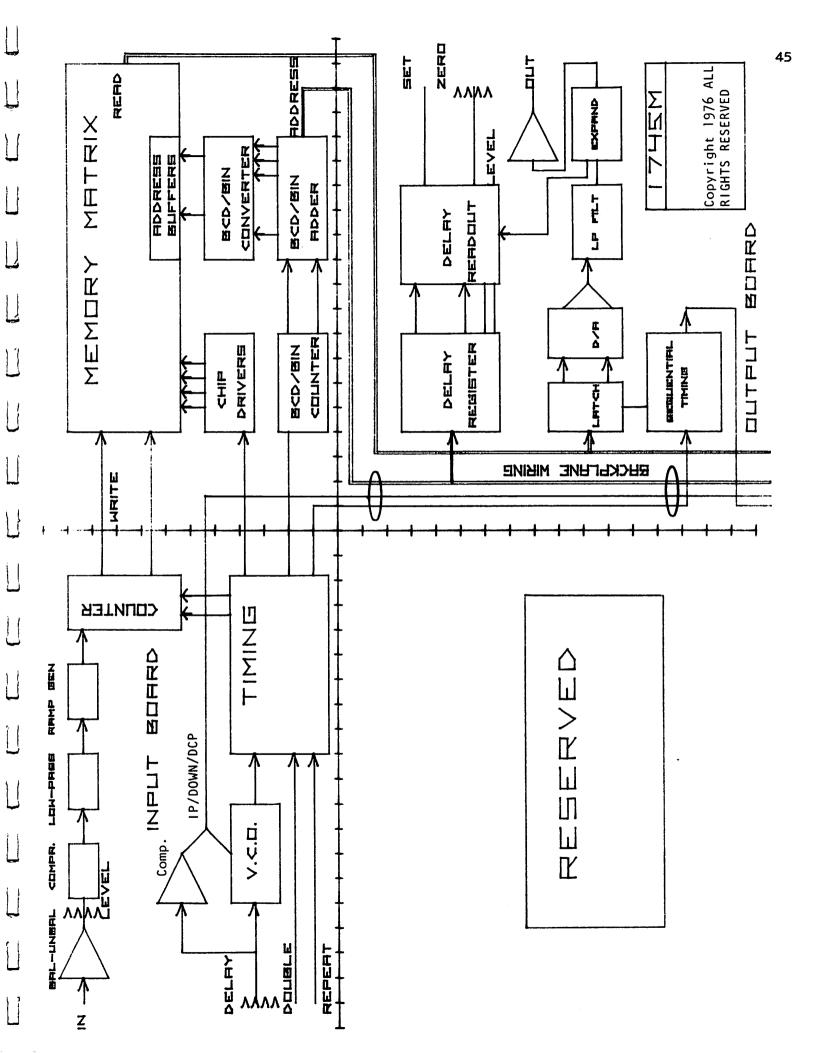

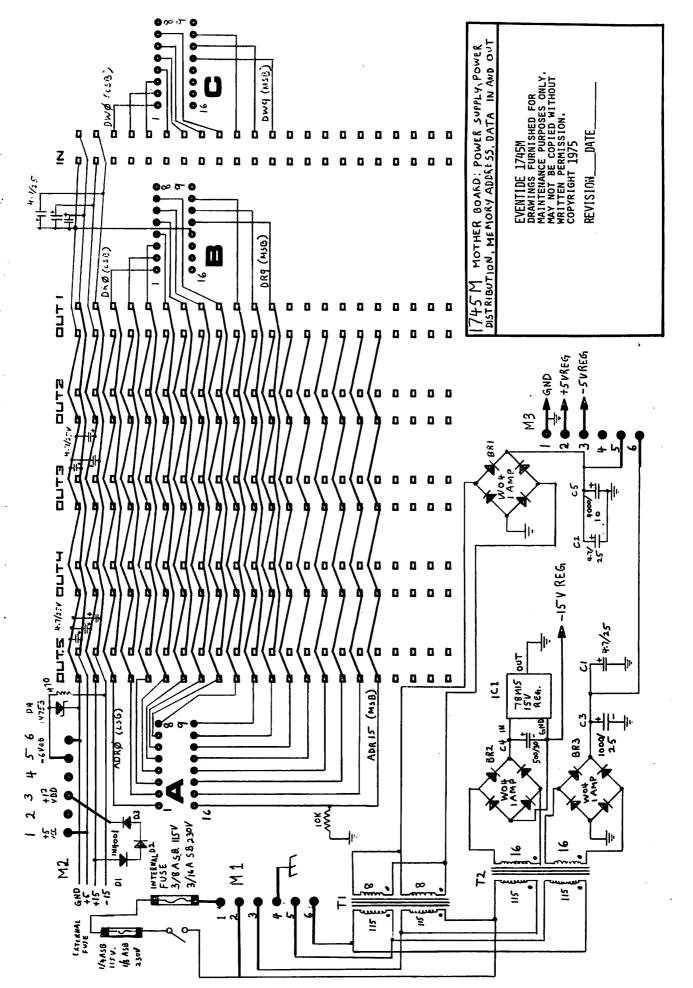

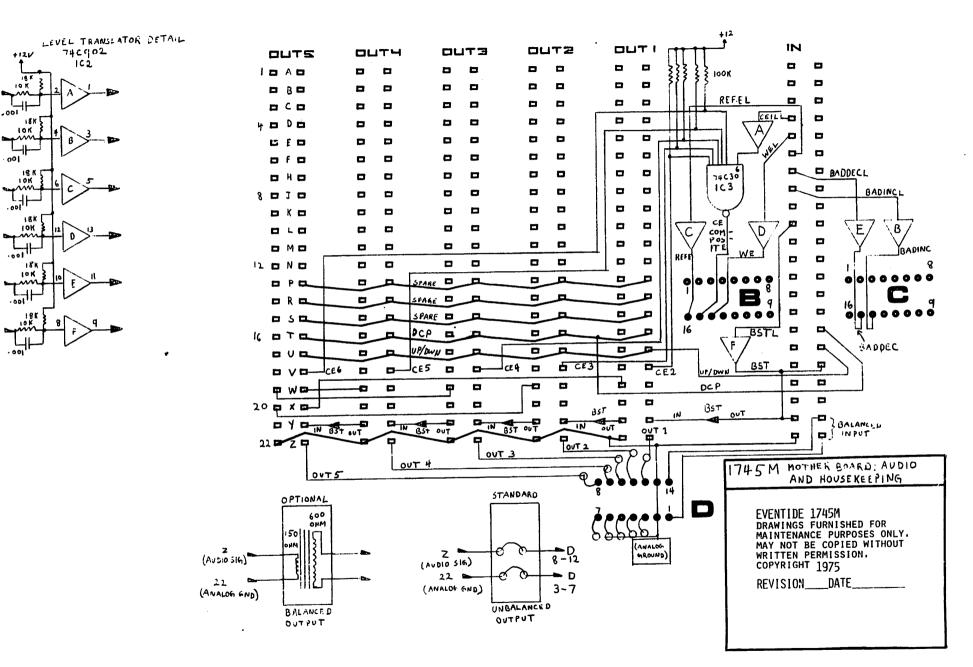

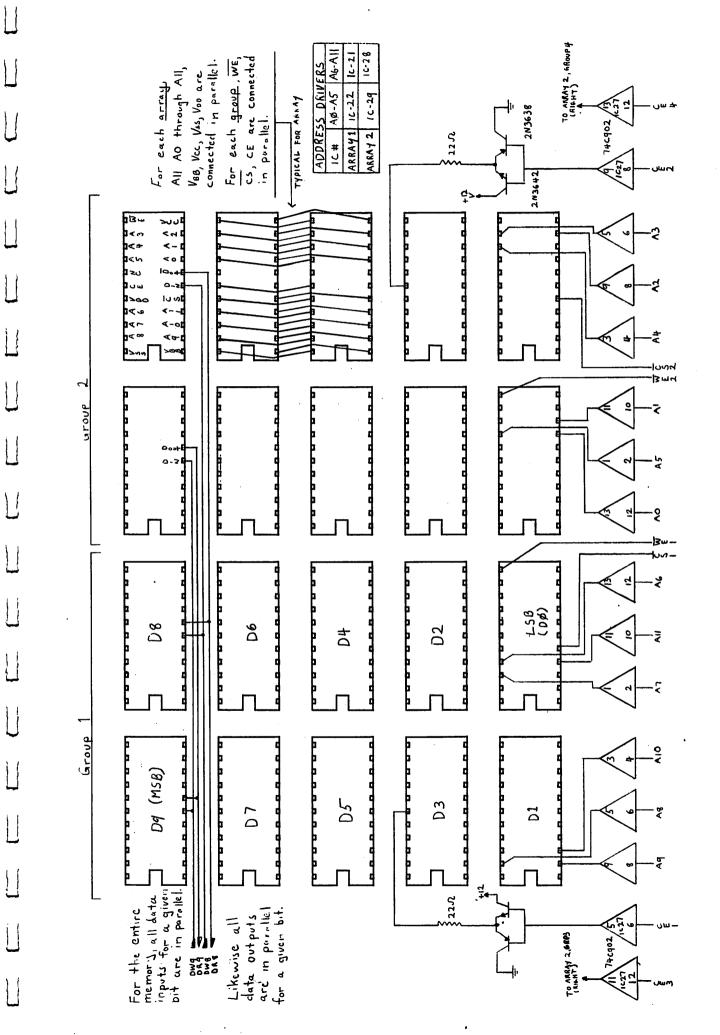

| DRAWINGS:                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Mother Board Parts Location<br>Chassis Wiring and Cable Assemblies<br>System Block Diagram<br>Mother Board Power Supply, Data IN/OUT<br>And Address Wiring<br>Mother Board Audio and Housekeeping<br>Mother Board Audio and Housekeeping<br>Mother Board Wiring List<br>Random Access Memory Board Array Wiring<br>Random Access Memory Board<br>Input and Timing Board<br>Output Board                                                                       | 43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52                         |

| Control and Readout Plug-In Boards                                                                                                                                                                                                                                                                                                                                                                                                                            | 53                                                                               |

| System Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54                                                                               |

| APPENDIX:                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

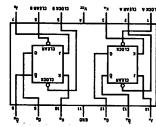

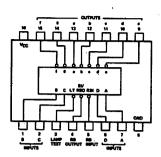

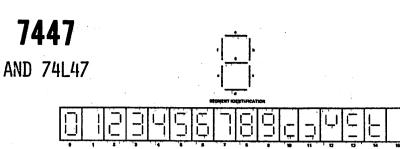

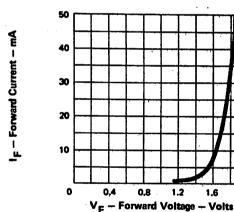

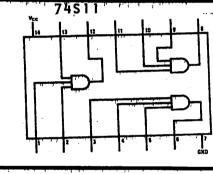

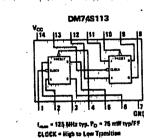

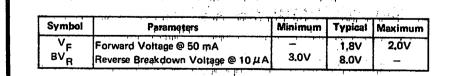

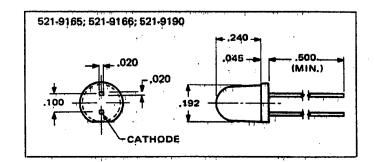

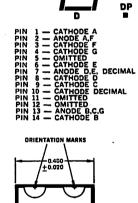

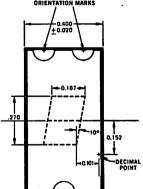

| Troubleshooting techniques<br>What to Do if All Else Fails<br>Integrated Circuit Pinout Diagrams<br>CMOS<br>Random Access Memory<br>Arithmetic Units, ECL<br>LED's, Schottky, Decoder Drivers                                                                                                                                                                                                                                                                 | 55<br>59<br>60<br>61<br>63<br>64                                                 |

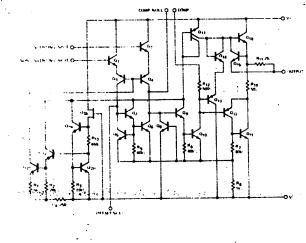

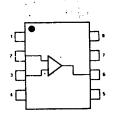

| Linear Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65                                                                               |

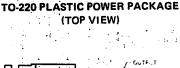

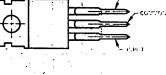

| Voltage Regulators, D/A Converter                                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                                                               |

#### INSTRUCTION MANUAL MANUAL

Of necessity, this is an unusual instruction manual. Most audio engineers are familiar with audio equipment, and, of course, the Model 1745M digital delay line is a piece of audio equipment. However, except for a very small portion of the internal circuitry (the input and output amplifiers) the delay line will be unfamiliar to most people whose experience has been exclusively in the audio field.

Inside the DDL, many "state-of-the-art" technologies are employed. There are operational amplifiers, MOS RAM's (random access memories), analog to digital converters, CMOS integrated circuits, light emitting diodes and displays, binary to BCD and back again converters, and some rather densely packed double sided printed circuit boards (with plated through holes yet.) Although the design is straightforward, the schematics are replete with unfamiliar (to audio people) symbols and signals with names and strange properties.

Therefore, this manual is organized into two sections. The first section is the operating manual and contains data on what goes into the delay line and what comes out of the delay line: (audio, pure and simple). This section also contains help-ful operating hints, application notes, and anything else which in our opinion will be useful to the engineer responsible for using the equipment. This section also contains a primer in the form of magazine articles which discuss in general form the technology behind the DDL.

The second section is the service manual. While we hope that the unit will not require servicing, we recognize that any device may fail, and more complex devices are more likely to fail than simple amplifiers or equalizers. The delay line rates as a complex device, containing as it does on the close order of 200 integrated circuits, many of which are are the equivalent of over ten thousand transistors! If that is not impressive, consider a pile of transistor radios the size of the great pyramid of Cheops. That *is* impressive. Irrelevant, but impressive. The service section contains complete technical information about the delay line, including schematic and block diagrams, theory of operation, troubleshooting suggestions, and an appendix. The appendix purports to teach some of the rudiments of digital troubleshooting to engineers familiar with audio techniques, but unacquainted with digital technology.

Copies of Section One are supplied with relative abandon, both with rental units and to prospective purchasers. Copies of Section One may be purchased for \$2.50 each, refundable on purchase. Copies of Section Two are serialized and zealously guarded by a battery of white-lipped attorneys fallen on hard times. The timberwolves were released when the price of flesh exceeded the price of food. Additional copies of Section Two may be purchased for \$25.00.

This manual covers the standard 1745M delay line, which contains the basic complement of circuit cards. Additional cards will be brought out from time to time, and information about these optional cards will be contained in separate addenda. Information on adding additional standard outputs is contained in this manual, however, and no additional manual is required when ordering them.

|                                           | SPECIFICATIONS: MODEL 1745M                                                                                                                                                                                                                                                                                 | 3    |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| INPUT LEVEL                               | Adjustable by front panel control10 to +16dbm<br>nominal for full output level as evidenced by illum-<br>ination of red LIMIT indicator                                                                                                                                                                     |      |

| OUTPUT LEVEL                              | Clipping level +18dbm. Screwdriver adjust control<br>accessible from front panel available for small adjust-<br>ments.                                                                                                                                                                                      |      |

| IMPEDANCES                                | INPUT balanced electronically, each line nominal 4.7K in series with 1000pf to ground. 600 ohm xfmr optional 0UTPUT unbalanced, 150 ohms nominal. Transformers are optional, and increase maximum output to +22dbm. Without transformers, input should not exceed 40V p-p, or $\pm$ 12V p-p on either line. |      |

| FREQUENCY RESPONSE                        | <u>+</u> ldb, 30Hz-16kHz. Extremely rapid rolloff after 16kHz.                                                                                                                                                                                                                                              |      |

| DISTORTION                                | Less than .3% THD from just below clipping to -10dbm<br>output between 100Hz and 10kHz. Less than 1% over<br>remainder of frequency range.                                                                                                                                                                  |      |

| DYNAMIC RANGE                             | Greater than 90db between minimum usable signal and<br>clipping level. Solid state indicator flashes red<br>nominally 3db below clipping, green nominally 12db<br>below clipping, and yellow when signal is present.                                                                                        |      |

| DELAY CHARACTERISTICS                     |                                                                                                                                                                                                                                                                                                             |      |

| DELAY                                     | Variable in 20 microsecond steps to 319.98 milliseconds<br>Variable in 40 microsecond steps to 636.96 milliseconds<br>in DOUBLE mode, reduced frequency response.                                                                                                                                           |      |

| DELAY MATCH                               | When outputs set to identical delay, adjacent output<br>relative delay less than 3us.                                                                                                                                                                                                                       |      |

| MINIMUM I/O DELAY                         | Less than 40us.                                                                                                                                                                                                                                                                                             |      |

| SHORT TERM STABILITY<br>(wow and flutter) | .001% (1 part in 10 <sup>5</sup> averaged over 100 ms interval)                                                                                                                                                                                                                                             |      |

| LONG TERM STABILITY                       | .01%/month.                                                                                                                                                                                                                                                                                                 |      |

| ACCURACY                                  | Readout accurate to nearest millisecond. Optional read gives delay to nearest lOuSecond. Accurate to .02%.                                                                                                                                                                                                  | lout |

| PHYSICAL CHARACTERISTICS                  |                                                                                                                                                                                                                                                                                                             |      |

| HEIGHT<br>WIDTH<br>DEPTH BEHIND PANEL     | 13.34cM (5-1/4") standard rack dimension*<br>58.26cM (19") standard rack dimension<br>38.10cM (15")                                                                                                                                                                                                         |      |

|                                           | *Normally supplied with rubber feet for tabletop mounti<br>Feet may be removed for rack mounting.                                                                                                                                                                                                           | ing. |

| POWER REQUIREMENTS                        | <pre>115VAC, 50-60Hz, nominal 25VA. May be internally wired<br/>for 230VAC, 50-60Hz.</pre>                                                                                                                                                                                                                  | ł    |

U

Ľ

Ĺ

Ľ

5

IJ

U

ال

Ľ

Ľ

-

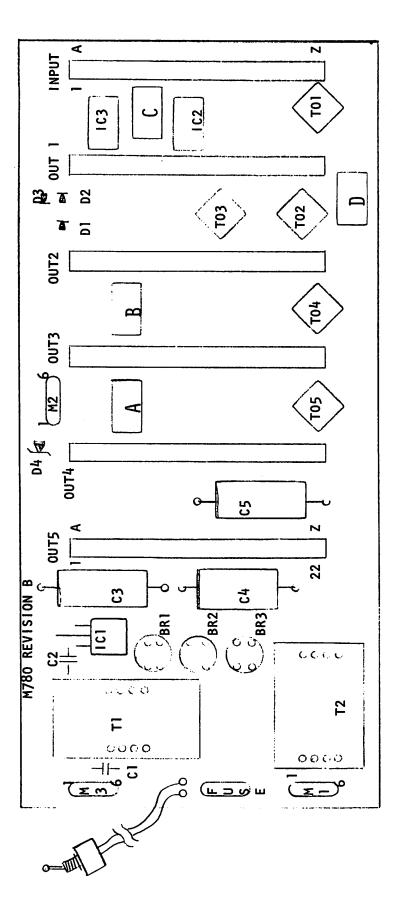

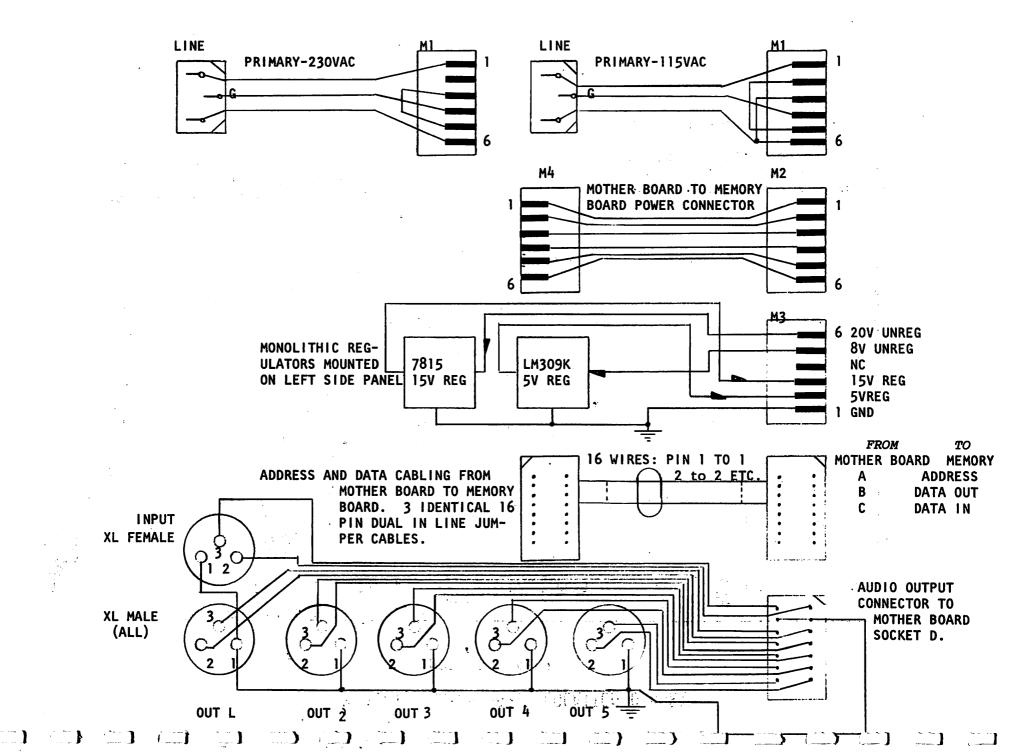

## INTERCONNECTION

The 1745M is capable of containing 1 INPUT module and up to 5 OUTPUT modules.

Each module position is represented on the rear panel by one 3-conductor audio connector. These connectors employ the following wiring convention:

#### BALANCED CONFIGURATION

|           | INPUT                                                    | OUTPUT                     |  |

|-----------|----------------------------------------------------------|----------------------------|--|

| PIN 1     | Connected to analog ground                               | Connected to analog ground |  |

| PIN 2     | Input, -phase                                            | Output, -phase             |  |

| PIN 3     | Input, +phase                                            | Output, +phase             |  |

| IMPEDANCE | Either HI or 600 ohms depen-<br>ding upon input resistor | 600 ohms                   |  |

|           | any upon input resistor                                  |                            |  |

#### UNBALANCED CONFIGURATION

|                                      | INPUT                                                              | OUTPUT                                                                                  |  |

|--------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| PIN 1<br>PIN 2<br>PIN 3<br>IMPEDANCE | Connected to analog ground<br>Input, -phase<br>Input, +phase<br>HI | Connected to analog ground<br>Connected to analog ground<br>Output, +phase<br>150 ohms. |  |

|                                      |                                                                    |                                                                                         |  |

.....

Input connector is female type D3F. Mating cable connector is type A3M. Output connector is male type D3M. Mating cable connector is type A3F. Part numbers are Switchcraft. Equivalent connectors are made by Canon and others.

## **DISPLAY BRIGHTNESS**

The delay line is furnished with the displays set at what we believe to be optimum brightness for typical studio applications. The display brightness can be increased or decreased by about 50%.

- To INCREASE BRIGHTNESS: Remove DDL top cover and place shorting link across diode in series with PIN V of the readout board socket.

- To DECREASE BRIGHTNESS: Remove DDL top cover and connect additional diode in series with diode going to PIN V of the readout board socket.

- Caution: Do not decrease brightness by more than one diode to prevent marginal operation of decoder IC's. Do not increase brightness if more than 3 outputs with readouts are installed to prevent possible power supply overload.

MAIN FRAME

INPUT MODULE CONTROLS AND INDICATORS

The POWER switch is the only control not associated with a particular plug-in module. This control applies AC power to the entire unit. The FUSE receptacle is connected in series with the POWER switch and an additional internal fuse. To protect the unit, the correct fuse must be installed, as per the following table: VOLTAGE: 115VAC 230VAC INTERNAL 3/8Amp 3/16Amp 1/4Amp EXTERNAL 1/8Amp To replace the fuse, press the bottom of the insert until the top pops forward.

The GAIN control is used to adjust the input level to the delay line. Full clockwise rotation allows signals of approximately -10dbm to achieve full dynamic range. Full counterclockwise rotation cuts off the input signal.

The three colored light emitting diodes in the LEVEL block on the Plexiglas panel indicate the relative input level. The RED lamp becomes illuminated approximately 3 db before the input signal reaches the clipping level (LIMit). The GREEN (NORmal) lamp becomes illuminated approximately 12 db before the input signal reaches the clipping level. The YELLOW SIGnal present lamp becomes illuminated when there is any significant signal applied to the input.

The spring return REPEAT switch allows the signal present in the delay line's memory to be captured and repeated. Momentarily deflecting this control upward activates the feature, and momentarily deflecting it downward de-activates the feature. An orange RPT light emitting diode in the Plexiglas panel becomes illuminated when the DDL is in the REPEAT mode.

The spring return DOUBLE switch causes the input sampling rate to be cut in half by discarding alternate samples. This halves the rate at which data are written into the memory, and thus doubles the total delay time. An orange 2X light emitting diode in the Plexiglass panel becomes illuminated when the DDL is in the DOUBLE mode. When this LED is on, the correct delay of each output is equal to twice the amount indicated in the associate readout. The switch operates in a manner similar to the REPEAT switch: press up to activate, down to de-activate.

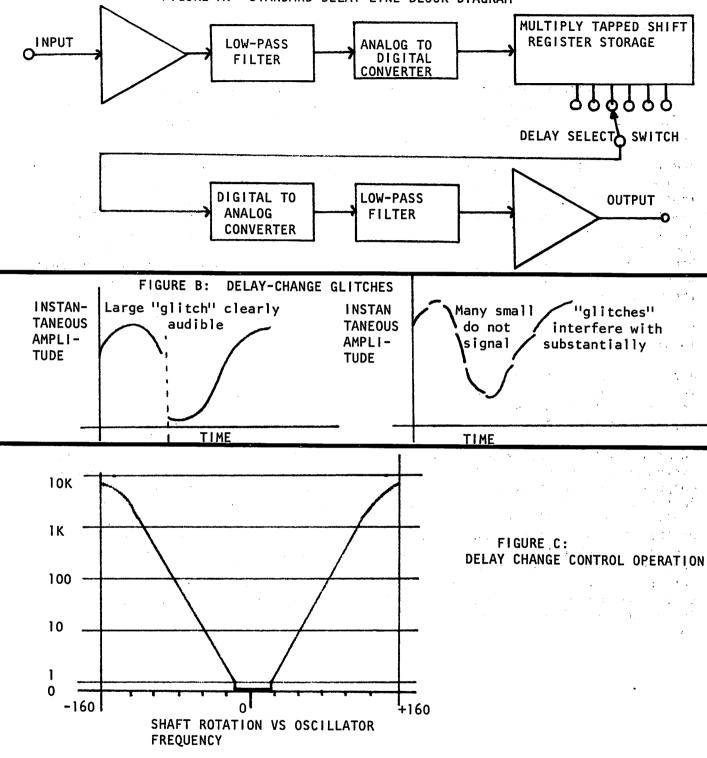

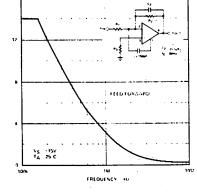

The DELAY control activates a wide range oscillator which switches the delay in small steps, one step per pulse. This oscillator is disabled when the knob is aligned with the arc divider. As it is rotated in either direction, the oscillator frequency increases logarithmically. At the extremes of rotation, pulses are produced at a rate sufficient to traverse the entire delay length in approximately 3 seconds. At the slowest setting, the delay varies at about 1 step per second. A graph showing the control setting *versus* delay change rate is shown at left.

1

11

11.

A steering signal is also produced by the control which determines whether the delay is to increase (CW rotation) or decrease (CCW rotation).

The delay change process is nearly inaudible, except at the extremes of rotation, at which point the output signal appears to suffer a pitch and tempo change. In order to get a feeling for the action of the control, it is recommended that the instructions in the FLANGING application section be followed.

Each output module has facilities for independent delay adjustment (under control of the DELAY control described above) and level.

The switch marked SET/ZERO tells the module to accept the oscillator signals when in the SET position, or to ignore them in the center off position. Each module may be set independently by placing the switch in the SET position, adjusting the delay with the DELAY oscillator and then centering the switch and proceeding to the next module.

Each module may be independently ZEROED by momentarily deflecting the switch downward. (This is a spring-return position.)

Each module has power-up-clear circuitry to reset the delay to zero upon application of power. If more than one module is in the SET position and the DELAY control is not centered when power is turned on, it will be noted that, after a short delay, the outputs will begin to count. Because there is a time delay involved which is different for each module, the outputs will not track precisely, nor should they be expected to. In general, the outputs will only track precisely when they have been in the SET position the same amount of time, and subject to the same number of oscillator pulses. It requires 50 pulses for the readout to change by 1 ms.

The readout indicates, to the nearest millisecond, the delay at which the output is set. If the delay is less than 10 milliseconds, only one digit is illuminated, if less than 100 milliseconds, only two digits are on. The readout will reset above 319 to 0, and below 0 to 319.

#### INPUT LEVEL SETTINGS

The Eventide Digital Delay Line is similar to amplifiers, equalizers, tape recorders, and virtually every other electronic device with the possible exception of a piece of wire at absolute zero in that it has a certain, limited, *Dynamic Range*. Dynamic range is defined as the levels between which operation of the of the device in question is useful or acceptable. As a practical matter, the range is usually bounded on the high side by excessive distortion, and the low side by excessive noise. In many equipments, a level indicating device such as the familiar VU meter is provided to indicate when the unit is operating at the proper level. A tape recorder, for instance, has a certain percentage of distortion at OVU, and this percentage rapidly increases as the signal level increases. The noise level is some number of decibels below OVU. This number of decibels is defined as the DYNAMIC RANGE.

Signal sources typically have a dynamic range much greater than that of electronic devices. Likewise, the ear can hear a dynamic range much greater than that of electronic devices. Since the electronic device (the Delay Line in this case) is the limiting factor, it is obviously a good idea to set the operating level of the delay line to take advantage of the maximum dynamic range of which it is capable. This is the equivalent of making sure that the meter on a tape recorder is reading around OVU most of the time.

Ĺ

L

Ũ

To enable accurate setting of input level, three solid state lamps have been provided on the front panel. The lamps are arranged in a column, yellow on the bottom, green in the middle, and red on the top. The DDL is adjusted internally so that, at IKHz input frequency, the red light will come on nominally  $\frac{1}{2}$  db below the point at which both the analog and digital portions of the unit approach the clipping level. This corresponds to an analog signal level of about +14dbm into 600 ohms. A momentary red flash of the indicator shows that the system dynamic range has been momentarily approached or exceeded. Continuous operation of the red indicator on program material is indicative of severe distortion.

The green light will come on at a level approximately 12db below the clipping point, and indicates the normal signal range at which the delay line should operate.

The yellow light comes on when any signal is present, even at a very low level. This is an aid in making sure that the unit is properly connected, and that a signal is present. It will be on almost continuously during proper operation.

ALTHOUGH THE RED LIGHT INDICATES THAT THE DELAY LINE IS ON THE VERGE OF CLIPPING, IT IS DESIRABLE TO OPERATE THE UNIT WITH THE RED LIGHT FLASHING INTERMITTENTLY!

The internal signal processing circuitry assures that, with normal program material, intermittent flashing of the red light does not mean that the signal is being significantly distorted. This is important to understand, because most signals will have some peaks which are much greater in amplitude than the average level, and attempting to preserve these peaks faithfully results in a serious compromise in dynamic range. In operation, it will be found that the red light flashes more frequently as the DDL is connected closer electrically to the microphone, and that it can flash more frequently when so connected before the distortion becomes objectionable. This is so because other equipments in the audio chain have similar peak clipping properties. (And, of course, the ultimate limiting factor is the tape or disk.)

When the GAIN control is properly adjusted, the green light will be on most of the time, and the red light will be flashing intermittently. This flashing may be anywhere from several times per second to once every few seconds. The table below gives a rough indication of proper settings.

| INPUT LEVEL SETTING CRITERIA  |                   |                  |                                 |

|-------------------------------|-------------------|------------------|---------------------------------|

| TYPE OF SIGNAL AND SOURCE     | YELLOW DUTY CYCLE | GREEN DUTY CYCLE | RED DUTY CYCLE                  |

| Integrated program (radio)    | 100%              | 80%              | once per 2 sec                  |

| Integrated program (live mix) | 100%              | 50%              | once per second                 |

| Voice (talking)               | 75%               | 30%              | once per 2 sec                  |

| Piano                         | 100%              | 30%              | 2-3 per second                  |

| Guitar, acoustic              | 75-100%           | 30%              | 2 per second                    |

| Guitar, fuzz                  | 100%              | 60%              | l per second                    |

| Synthesizer                   | 80%               | 80%              | infrequent                      |

| Organ                         | 80%               | 80%              | infrequent                      |

| Drums                         | 75-100%           | 20-70%           | once per well-<br>defined beat. |

All the above numbers are approximate. They will vary widely if the signals are pre-processed through limiters, equalizers, or any other amplitude-distorting processor.

In general, it is not necessary to be very critical about the level setting, any more than it really matters if you record at +1 or -1. However, it is always good practice to get the most from your equipment, and the above settings will give you the most dynamic range. For most applications, the DDL's 90db dynamic range will not be the limiting factor in the signal chain.

#### DELAY DOUBLING

As much as we'd like to, we cannot furnish a 640 millisecond delay line for the price of a 320 ms unit. There ain't no such thing as a free lunch, and RAM's cost more than munchies. We can, however, do the next best thing: We have put a switch on the front panel which says "DOUBLE", and turning this switch will double the delay capacity of the 1745M. *BUT*, at the same time, the frequency response is degraded. In other words, in the DOUBLE mode, we do not consider the 1745M to be a studio quality unit.

U

Ú

U

The reason for this degradation is inherent in engineering arcana known as "sampling theory", discussed a bit more technically later on. Suffice it to say that the DDL looks at the incoming signal at a certain rate known as the "sampling rate", and transmits these samples through a delay to the output. In the DOUBLE mode, alternate samples are ignored and are not sent to storage. Since the storage capacity remains constant, it is only filled half as fast, and so will store the signal twice as long, thus doubling the delay. However, since the samples are taken less frequently, anything occurring between samples (*i.e.*, during the sample which was ignored) is discarded. In practice, this means that high frequency signals greater than about lOkHz are subject to heterodyning and various forms of distortion. High frequency sine wave tests produce truly weird results. Fortunately, normal program material does not contain high frequency sine waves and so is only slightly modified. The major difference between modes shows up as a harshness in the treble register. Much of this can be eliminated by EQ'ing down the highs on both input and output, at the further expense of frequency response.

Don't let the foregoing scare you into not using the delay doubling feature. Despite the harshness, program quality is perfectly acceptable except for fairly critical listening. Speech, especially, is relatively unaffected by delay doubling, as are other signals which do not have a large high frequency content.

#### APPLICATIONS

The DOUBLE provision is primarily of use in instances where greater than 320 milliseconds of delay is required and less than optimum quality can be tolerated. Sound reinforcement applications particularly suggest themselves due to the normally present high frequency attenuation of the atmosphere, and the fact that it's rarely possible to listen critically to a PA speaker. The harshness at high frequencies will usually be inaudible if there is any masking signal present.

Other applications which suggest themselves are special effects and communications uses in which the signal channel parameters will be more limiting than the DDL response. Many of the uses of the DOUBLE mode occur in conjunction with the REPEAT mode. For instance, a signal can be "captured" in the DOUBLE mode and then recirculated in NORMAL. If this is done, it will be played back twice as fast, for a nice Mickey Mouse effect, or a substantial aid to spectrum analysis and voice printing. Further applications will be discussed after the recirculation section of this manual.

#### REVISITED

Remember when the Digital Delay Line was new? You don't have to go back too far in the audio business to remember the first DDL, complete with such exotic concepts as an Analog to Digital converter, magnetostrictive delay lines, antialiasing filters, and such marvelous arcana as *bits* and *clocks* (which didn't even tell time).

Well, if you've been awake in recent years, you know a bit about digital technology by now. Your watch is digital, you have a digital calculator (or pocket computer for a few extra bucks), your voice is frequently digitized on the telephone, your tape machine searches digitally, and you may have even learned to count on your fingers. Of course, if you've done any mixing or sound reinforcement work, you've undoubtedly used a digital delay line for the special effects or time synchronization of which it is uniquely capable. Somewhat less likely, you've had occasion to delve into the electronic circuitry by which these units achieve their delay. The DDL is "transparent" to the end user, i.e., an audio signal goes in, and an audio signal comes out somewhat later. Absent curiosity or malfunction, there is no need for the user to know what goes on inside the unit. Ask a non-technical person what is going on inside a DDL, and he will probably make some reference to Analog to Digital converters, Shift Registers, and Digital to Analog converters. Don't ask any further questions as they will probably lead to mild embarrassment. They needn't, though, because that last sentence is a fair summary of what really does go on in a DDL. After a brief flirtation with magnetostrictive delay lines (very clumsy mechanical delay lines), the industry universally adopted the integrated circuit shift register as its method of storing signals to be delayed.

Very briefly, the principle of operation of the DDL is this:

- 1: An audio signal is low-pass filtered to eliminate super-audible signals which could cause beat notes and spurious outputs.

- 2: The signal is then converted into a digital format at a rapid rate, typically 25 to 50 thousand times per second. Each of these 25K to 50K samples is represented by a digital word, which consists of a group of "l's" and "0's". The word represents a specific voltage level as present in the original signal.

- 3: This word is *clocked* into a digital storage medium, such as a semiconductor shift register, in which it is progressively moved towards the output, one storage location per clock or sample period. The delay is thus determined by the clock rate and the number of storage locations available by the rather simple relationship

DELAY= Number of storage locations Clock or Sampling frequency <del>تن</del>م

11

-

- 4: After the digital word reaches the output of the shift register, it is reconverted to an analog format and again filtered to remove spurious frequencies, this time primarily associated with the sampling clock.

- 5: The signal, thus converted and delayed, is conducted to the outside world, ready to begin its career.

The above admitted oversimplification completely ignores the differences between delay lines from different manufacturers, which are primarily related to methods of encoding the analog signals into digital format, and the various control features of the competing units. The method of signal processing determines the dynamic range of the unit: depending upon the application, ranges of from 40db to over 90db are desirable, and it makes little sense to purchase more range than required because the cost is directly proportional to the dynamic range, as both the amount of storage and circuit complexity increase with increasing dynamic Likewise, units are available with delay switchable in narrow increments range. with great facility, to those in which delay is completely fixed at purchase. Naturally, you pay for control features, and for delay time. The third major trade-off is frequency response. Within narrow limits, the frequency response is about 1/3 the sampling rate. Doubling the sampling rate doubles the rate at which the digital samples pass through the shift registers, and thus cuts the delay time in half. So, one would expect a given delay line to give half as much delay at 50kHz as at 25kHz. It is possible to compromise, however, so that a given delay line may have variable or selectable clock rates to allow longer delays when wide frequency response is not necessary, such as in some special effect or sound reinforcement applications.

With all these differences, there has been one unifying and limiting factor in DDL design: All units have used the shift register as a storage medium. To see why this is limiting, let's look at the shift register:

The shift register is a serial storage device. It comes in various lengths, from 4 bits to several thousand bits. New technology has recently made l6kilobit registers possible. At first glance, it would seem that shift registers are ideal for delay, because of their very structure. They work by transferring a packet of charge representing a digital 1 or 0 from one internal node to the next. No additional timing circuitry is necessary-the registers accomplish the delay all by themselves. Furthermore, they may be connected in series to achieve longer delays, and the points at which they are connected can be used as delay taps. If each shift register provides, for example 10 milliseconds of delay, and 20 are connected in series, 200 milliseconds are available in 10 millisecond steps. As a practical matter, many parallel shift registers are required to handle a full word, and the switching becomes cumbersome after a few taps are necessary. There are many techniques for circumventing this problem which add only minimal complexity to the entire system. So what's the problem? Well, consider how to vary the time delay. There are two basic choices: one is to switch shift register taps; the other is to vary the clock rate. Switching taps creates discontinuities in the signal. Looking at a signal at point A and point B at, say, 1 millisecond time difference creates a sharp transient at the splicing point (see figure B). Even if the switching is accomplished electronically, such as with an optical encoder and digital multiplexers, this transient is unavoidable, except when the signal level is zero, or the points to be joined coincidentally have the same amplitude. If the delay is to be changed rapidly, this becomes a serious detriment, as many of these splices add noise to the signal. Varying the clock rate overcomes this problem, but creates another one, the inability to vary the delay by more than a certain percentage. The upper limit of variation is governed by the allowable decrease in frequency response; the lower limit by the capability of the A to D converter and the timing circuitry. A typical variation of 50% is insufficient to change from short to long delays, and since all outputs vary by the same percentage, it is impossible to vary one output with

respect to the other. The basis of the flanging effect is the sliding of one signal past another in time, and so this lack of capability is a great disadvan-tage.

One solution to the above problems would be to have shift registers with taps every sample. So doing would enable one to switch from tap to tap rapidly while encountering only insignificant splicing noise (Fig. B). This is because, with normal program material, the amplitude difference between successive samples is very small. Switching between samples in this manner produces at worst a low amplitude tone at the switching rate which is effectively masked by the signal. The only time you run into trouble with this method is varying the delay of high frequency deterministic signals, which is very unlikely in normal circumstances. Unfortunately, tapping shift registers at every bit would require a maze of wiring large enough to fill an ordinary city dump, and the equipment would end up there after one repair was attempted. (It is possible to use combinations of shift registers to achieve an arbitrary delay time, but this is not the same and will not work, just in case anybody is tempted to try. The reason it won't work is that in switching individual shift registers around, it becomes necessary to wait for them to fill up, which can take an arbitrary length, much greater than one sample, before the output is usable.)

Another solution to the above problem is to use Random Access Memories. This solution does work, and is described starting now.

#### Description of Random Access Memories

A random access memory is a semiconductor chip (or assemblage thereof) which can store individual chunks of data, and deliver them up upon command. They differ from the shift register in that any of the stored data is immediately available regardless of when it was entered into the memory. If the shift register is compared to a pipeline, the RAM may be compared to a book, in which each page is numbered and accessed without reading its neighbors. In digital terminology, the "page numbers" are "addresses", and an individual RAM integrated circuit may have from 16 addresses, as used in either very old or very fast chips, up to 4096 addresses as used in many of the newest computers. Assuming each address location holds 1 bit, it is obvious that one "4KRAM" is the equivalent in storage capacity of four industry standard 1K shift registers. Of course, nothing exists in a vacuum, and the 4KRAM must be economically viable, available, and reliable. Fortunately, this is the case, as the price of the 4KRAM, which was astronomical until mid 1975, is now in the range where it is reasonably comparable to the price of the shift registers which it replaces. Anticipating the price reductions, we began the design of a Digital Delay Line using random access storage instead of shift registers. Some of the details of the design, and the possibilities of RAM's are described below.

To begin with, getting delay from a memory is a bit more involved than getting delay from a shift register. To allude to the book vs. pipeline analogy, if you put something into a pipeline, you need only wait for it to come out. The delay is equal to the length of the pipeline. If you wanted to get delay from a "book", you would have to read the data a certain number of pages after the beginning. Since this is a dynamic process, the point at which the data atewritten also must vary. (If it did not, data would be overwritten at the same location. Look at an old piece of carbon paper and try to imagine what that would *sound* like!) Therefore, the way to get delay from a memory is to employ a *pointer* or *base address* register. Every time a new sample is written into the memory, the register is decremented (decreased by 1). This register then points to the location of the most recently written data. Since the register is decremented once each sample period, adding 1 to the register contents points to a sample that is delayed by a sample period. If the sampling rate is 50KHz, then, each sample is 20 microseconds delayed from the previous one, and if data are being written at address #150, then data being read at address #200 are delayed by 1 millisecond. Fortunately, the actual numerical address is irrelevant, as all data storage locations are identical. Thus, an output can be obtained at an arbitrary delay simply by generating a number equal to the number of samples difference between input and output. The "housekeeping" is taken care of by a single register and arithmetic unit located on the circuit board which contains the memory.

Most delay lines, especially those used in recording studios, have two or more outputs. Multiple outputs are especially desirable in those applications involving choral effects and reverberation. In order to accommodate multiple outputs, it is necessary to organize the system as a "bus", which means simply that several different signals can share the same physical connection. Doing this requires "3 state" logic, which differs from ordinary 2 state digital circuits in that not only can a 1 or a 0 be output, but the output also can be turned "off", in which case it assumes a high impedance. If multiple outputs are connected together, but only one is in a low impedance state, then the bus assumes the state of the low impedance output. By using modular output cards, and activating them sequentially, one can access several different addresses during any given sampling interval. The number of addresses which can be accessed is determined by the "access time" of the memory chip used and the sampling interval, which as stated above is 20 microseconds. Most common 4KRAM's have access times on the order of .2-.4 microseconds, which should be sufficient for 50 to 100 outputs. However, computing the proper address also requires time, and common TTL circuits, which are very fast, consume quite a bit of power. As one of the objectives of the design was to reduce power consumption, we used all CMOS circuitry, whose power consumption decreases almost to zero as its speed decreases. Even so, there is plenty of time to service up to seven outputs, and module positions are provided for up to five, leaving margin for extra functions.

Another problem arises in that RAM's are universally binary devices, and human beings are generally decimal. Some provision must be made to allow setting the delay (and reading it out) in human-decipherable units. Since each sample is 20 microseconds, one could simply convert the binary number representing the delay to decimal form and multiply by .020 to give milliseconds. Unfortunately, long binary to decimal conversions are slow or require much hardware. A far simpler solution involves using a small (0 to 999) decimal to binary converter, and doing all the output module addressing in decimal form. Each 4KRAM has binary addresses from 0 through 4095. Then memory locations 0 through 999 (binary) are addressed for the first 1000 samples of delay. If 1001 samples of delay (20.02 milliseconds) are required, the next address used would be binary 1024. In effect, for convenience, 96 addresses out of every memory are ignored and wasted. These addresses are still there, by the way, if needed, but it is a lot cheaper to waste them than to perform the conversions otherwise required. Using this system and sampling rate, a 16K memory, requiring 40 memory chips gives 319.98 milliseconds of delay in 20 microsecond steps, as compared to our previous system requiring 108 shift registers for 199 milliseconds, in 1 millisecond steps. A small additional advantage is that no extra shift registers are required for additional outputs. Assuming comparable reliability between the RAM's and shift registers, the memory design should be over twice as reliable. Furthermore, the industry has settled on two or three basic 4KRAM designs, and all are multiply sourced. We opted for the 22pin, nonmultiplexed address configuration for simplicity, and because space saving was not an urgent criterion. We have evaluated several manufacturers chips and found all but one acceptable. This, hopefully, will make delivery times independent of

### Silicon Valley idiosyncrasies.

One final unusual design feature: our 1745A delay line utilized an optical encoder (see January 1974 db magazine) for delay switching. This eliminated the need for coarse and fine delay controls and permitted fully incremental switching in 1 millisecond steps. The control had 20 lines, and produced 20 pulses per revolution, and could be spun to traverse the whole control range in one spin. To do the same with a unit which varies in 20 microsecond steps would require an encoder with 1000 lines. Although such devices are producible, and are used in precision mechanical systems, it was deemed impractical for reasons of cost and ruggedness. Instead, we designed an oscillator of wide frequency range with a small deadband in the center of its control range, and with parabolic control taper. The oscillator frequency range is from 1 Hz to 5kHz, which allows the full range of delay to be spanned automatically over several seconds to several hours. It should be noted that although the delay varies in 20 microsecond steps, the readout is only to the nearest millisecond. If one needs to know the precise delay, the information is available on data lines which may be connected to readout drivers. Other features of the 1745A were duplicated in relatively uninteresting ways. The delay double feature which allows doubling the delay at the expense of frequency response was implemented by inhibiting alternate base address decrementing pulses. The repeat feature was implemented by inhibiting memory write pulses, thus preventing overwriting old data and so saving them.

Superficially, then, we have a new delay line with a bit more delay and a whole bunch of familiar features implemented in a wholly new way. As stated earlier, the delay line is and should be transparent to the user in that, regardless of the implementation, you put audio in and get audio out. What does all this mean to the user?

Nobody would waste time with RAM's if it didn't mean something: of that you may be sure. It means:

That true flanging can be accomplished with a single digital delay line. The fine delay steps allow sweeping a variable output past a fixed output in tiny increments, thus giving an apparent continuous variation in tonality, as opposed to the step variations possible with other systems. Unlike analog delay flangers, the flanging may be performed after any fixed delay. Even "pre-flanging"is possible with a single delay line, by taking the flanging effect from the first two outputs and the dry signal from a third at greater delay. Of course, as with all digital systems, there is no degradation of signal to noise ratio as the delay is increased.

#### It means:

That continuous doppler shift or pitch change may be introduced into any signal simply by increasing or decreasing the delay in a continuous fashion (facilitated by the oscillator control). A rather long period of change is available before an artifact is introduced by the delay recycling from 319 milliseconds back to zero, and this can be minimized in certain ways involving interleaving more than one output.

#### It means:

That an auxiliary module which computes addresses in accordance with an appropriate program can be used to obtain an arbitrary pitch change ratio, and maintain that ratio. ANY ratio can be obtained. By proper address manipulation, it is possible to read audio out backwards! Think of that, special effects fans! And of course pitch change can be turned into tempo change in conjunction with a tape player.

It means:

That precise comb filters may be implemented with much finer control of delay. Since the system is crystal controlled, the delay time will not drift more than a few parts per million, and so a null can be set for some frequency and that frequency and its harmonics will be disappeared.

And that largely experimental applications, such as narrow bandwidth speech scrambling can be reasonably implemented. For instance, construct a card that will read out addresses 0 to 1000 normally, then jump to 5000 to 6000, then readout 2000 to 1000 backwards, etc, until the whole capacity is used up! Performing the inverse operation at a remote end will descramble the signal. The whole process, unlike digital encoding, does not significantly increase the bandwidth of the output, and thus it may be put on ordinary communications channels such as the telephone. This may also be an aid to communications, by using the memory delay line in conjunction with several filters, and setting each filter band at a different time delay. This is known as time-diversity transmission and can also be implemented with non-memory delay lines, but sure fits in with this paragraph.

And that experimental applications requiring digitized audio be available at various times can be implemented with a convenient test bed. Computer time need not be taken up implementing A to D routines and housekeeping. Samples may be withdrawn at any computed delay and used as the experimenter desires.

In addition to the above advantages, there is another capability built in to the system as a consequence of the memory bus architecture. If one can hang several outputs on a given bus, why not several inputs as well? Why not indeed! In fact one can, and so we did. The delay register inputs, normally set sequentially by the oscillator, can be set in parallel by placing the desired number on the address bus and strobing the output card which the engineer wants to set in the "dead time" between the last readout and a new sample. Provision has been made for a remote control module which enables precise setting of any or all outputs by digital control. Data may be furnished either from a remote console or from an automated mixdown system. Thus, another component can be operated in conjunction with automation, leaving the engineer and producer even freer to *listen*.

ARTICLE ILLUSTRATIONS

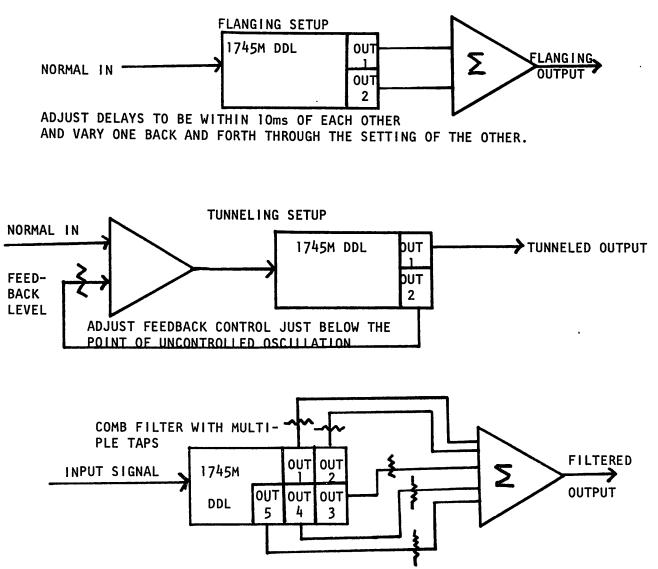

#### COMB FILTERS RECIRCULATION FLANGING TUNNELING PITCH CHANGING AND GENERAL WEIRDNESS

If you think that you just bought a delay line, think again.

In addition to delay, the unique control features and system architecture of the 1745M allow you to do all sorts of strange and wondrous things to your unsuspecting signals. The title of this page is a good beginning.

**CONBFILTER**

A comb filter is a device which has many frequency rejection notches or many peaks. Generally, these notches or peaks are evenly spaced, in a manner similar to the harmonics of a non-sinusoidal signal. A rudimentary comb filter can be made with a set of filters each adjusted to a different frequency, but this quickly becomes prohibitive, both in terms of cost and stability. A typical comb filter application is the rejection of interference in a broadband system. For instance, consider the case in which a tape made on location somehow picked up a tremendous 60Hz component. If only 60Hz is present, it can be nulled with a notch filter. More likely, however in addition to the 60 Hz, there will be 120Hz, 180 Hz, 240Hz, etc. components. SCR noise is notorious for causing such problems. Removing such noise from a tape can be accomplished with a comb filter.

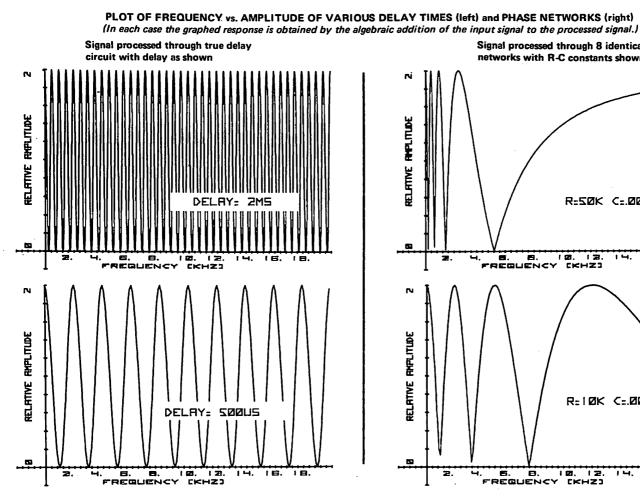

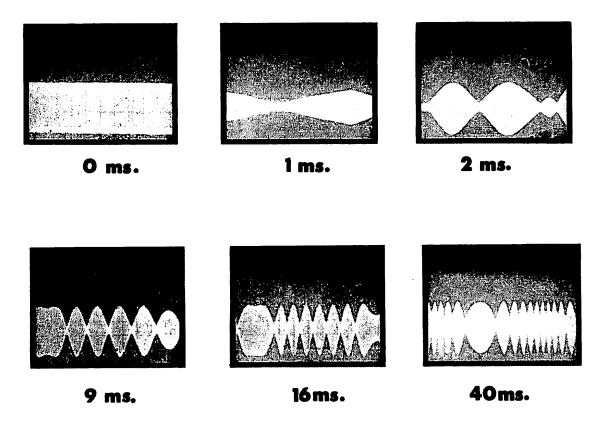

The basis of the comb filter is that, if a signal is added to a delayed version of itself, a regular pattern of nulls and peaks in the frequency domain is produced. (See graphs and scope photographs). The reason for this is intuitively clear: Assume a delay of 1 millisecond. Apply a 1kHz signal to the delay line input, and algebraically add the input to the output. Since the length of a single cycle of 1kHz signal is 1 ms, the input and output are in phase, and a 6db addition results. Now apply a 500Hz signal to the input. The output will be delayed by  $\frac{1}{2}$  wavelength, and out of phase addition will result at every point on the signal, creating a null in response at 500Hz. The amplitude at any frequency can be calculated by the following formula:

$H \doteq \frac{(T_d) (360)}{1/f}$

Where: f is frequency in Hz  $H= -T_d$  is the delay time in seconds

To null any given frequency and all of its harmonics, the delay time should be set equal to 1/F, and the input and output added out-of-phase.

To null any given frequency and all of its odd harmonics, the delay time should be set equal to 1/2F, and the outputs added in-phase.

The 1745M delay line is excellent for comb filter use, because it is adjustable in extremely small steps, all of which are crystal controlled and consequently stable typically to a few parts per million per day. Several outputs can be combined with different "weights" and different delays to establish different filter characteristics, including highly desirable narrow notches, which will null out given signals with very little effect on the broadband signals.

#### RECIRCULATION

A unique feature of the Eventide Digital Delay Line is its ability to "capture" a signal in its memory and to continuously repeat this signal through the outputs. Since the signal is stored digitally, there is no decay or noise build-up as would be present if some form of mechanical repetition such as a tape loop were employed.

The signal is captured by operation of the REPEAT switch as described in the control section. After a signal is captured, it may be modified by operation of the DOUBLE switch, which speeds up or slows down the repetition by a factor of 2. (If the signal was captured in DOUBLE, putting the DDL in NORMAL speeds it up, if captured in NORMAL, doubling slows it down.) In addition, if the DELAY control is operated, the pitch of the repeated signal may be changed either up or down. The total length of the signal captured is either 320 ms if captured in NORMAL, or 640 ms if captured in DOUBLE. This is long enough for several words, or a short rhythm pattern. By setting the outputs at different delays (or fixing one and varying another), the patterns or words may be caused to overlap, or appear to change sequence. Different psycho-acoustic effects may be obtained by placing the outputs in varying spacial and temporal relationships. Rotating and bouncing effects may be readily obtained.

An interesting effect is that obtained by listening to continuous repetition of a voice type signal. The signal may either consist of words, or word-like sounds. As the repetition continues, the meaning starts to disappear or shift, the words can change into nonsense (or *vice versa*), and other interesting psychological effects may be observed. This manual does not intend to delve into mysticism, but that shouldn't prevent experimentation.

More exotic applications include spectrum analysis for such purposes as voiceprinting and engine signature analysis. The delay line can convert an ordinary swept wave or spectrum analyzer into a quasi-realtime analyzer. Although it isn't by any means the equivalent of a realtime analyzer in terms of processing a large amount of signal rapidly, it can hold a captured signal indefinitely, permitting extremely detailed analysis of the captured portion. The signal is synchronous with the counting of the pointer register, described in the random access memory assembly circuit theory, and various weighting functions can be constructed or various features of the signal excerpted with great precision.

The REPEAT feature can be used to advantage in live performances. The repeat switch can be easily remoted, and control given to the performer by foot switch. Let the live signal come out undelayed or minimally delayed to prevent the performer from being distracted by an excessively delayed return echo. At various points in the performance (usually at the end of phrases or during prolonged vocal harmony notes) activate the REPEAT control and walk away from the microphone. If the performer can juggle, now is a good time to demonstrate it. When he is through, he can step back to the mike and continue.

#### FLANGING

Eventide manufactures, in addition to the DDL, a rather good INSTANT FLANGER (model FL201). It turns out, however, that the DDL can do a rather fine job of flanging all by itself. All that is necessary is to add the signals from two outputs together and then vary the delay of one up to and past the delay of the other. Because the delays can "slide" past each other, true flanging through 0 delay is realizable. Different effects can be achieved by adding the inputs in-phase and out of phase.

Because the effects created by the Flanger are so similar to those created by the DDL, we felt it would be appropriate to reprint from *Recording Engineer/Producer* an article originally reprinted from our Flanger manual.

Since its invention or discovery in the mid 1960's, the special effect known as "PHASING" or "FLANGING" has been one of the most popular additions to the mixer's repertoire. Phasing was introduced to the mass audience in the song "Itchycoo Park" by Small Faces and has been used (yes, and overused) to some extent by virtually every artist since that time. Just in case you've been on an interstellar voyage or in the Phillipine jungles since the 1960's, the phasing effect has been described by various individuals as "a swimming effect," as "a jet plane going through the music," as "a whooshing" sound, as "one of the best ways discovered to cover up mistakes," and as "something that makes you think the music is circling around you." All of these descriptions have merit.

The phasing effect's versatility can be partially explained by the following facts:

1. It affects three of the most important characteristics of a musical signalpitch, amplitude, and harmonic distribution.

2. It affects signals over a very wide frequency range, and thus applies to virtually every signal source from a bass guitar to a snare drum.

3. It produces dynamic changes in pitch, which is interesting in itself and can be used to cover up mistakes.

4. It can be used to generate a pseudostereo signal with interesting characteristics and little effort (pseudo quad too).

5. When used tastefully it can add a hell of a lot of interest to a recording or live performance. (When used without taste it can *still* add a lot of interest. Short of running an entire concert through a phasing device, it's hard to misuse.) WHAT IS PHASING?

#### WHAT IS FLANGING?

The terms "PHASING" and "FLANG-ING" have been used interchangably to describe the effect obtained. In point of electronic fact, there are two substantially different ways of obtaining the effect, and the effect thus obtained is also substantially different. The original effect (used on Itchykoo Park) was allegedly obtained by feeding a signal into two tape recorders, mixing the output, and then

placing a drag on one of the reel flanges to slow down the machine. Because this method ties up two tape machines, requires 22 patch cords, and is a bit awkward (how many engineers have calibrated fingers?), several manufacturers designed electronic "black boxes" to achieve the effect with greater ease. Typically these devices accept a signal input and produce a phased output, the phasing being controlled by front panel knobs. One manufacturer (Eventide Clock Works) designed a unit specifically for recording studio applications. This unit has several methods of controlling the phasing: in addition to a front panel " $\Delta \Phi$ " control, it has provisions for using an internal envelope detector or a variable frequency oscillator, thus phasing automatically either by following the signal amplitude or in a repetitive fashion.

However, (and it's a big however) . . .

HOWEVER these black boxes, for technical reasons, could not generate the same effect as the finger on the flange. And although the black boxes had many advantages which could not (and cannot) be duplicated by the tape flanging method, the effect was not as pronounced or "deep," and thus the tape method continued to be used when a particularly strong effect was desired. To prevent confusion, in the remainder of this article we will refer to PHASING and FLANGING by the following definitions:

PHASING: The effect obtained by using electronic phase-shift networks to generate cancellations in the frequency spectrum of a signal.

FLANGING: The effect obtained by using differential delay to generate cancellations in the frequency spectrum of a signal, regardless of the method used to generate the delay.

The difference in the sound of the two methods can be well explained by theory, and we proceed to do so below.

#### PHASING

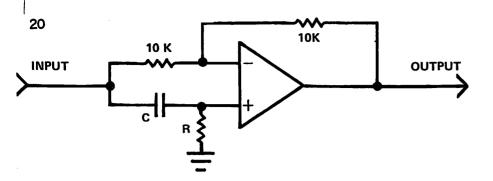

The basis of the "black box" phasing device is an electronic circuit known as

by RICHARD FACTOR\* Eventide Clockworks, Inc. New York, N.Y.

reproduced from Eventide's Model FL-201 'INSTANT FLANGER' instruction manual.

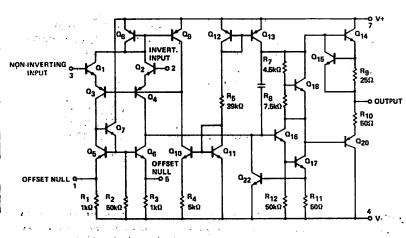

the "ALL-PASS NETWORK." As one might assume, this type of network passes signals of all frequencies, but its output phase versus input phase varies as a function of frequency. A representative circuit is diagrammed above.

Since the circuit has a single RC time constant, the maximum phase variation, assuming ideal components, is 180 degrees. In actuality, it can only approach this value since C is limited by stray capacitance and R must not exceed a reasonable value, depending upon the operational amplifier used. The output of the network sounds the same as the input (flat frequency response), but the phase is shifted according to the RC network constants. Thus, by adding the input of the network to the output of the network in a 1:1 ratio, the added signals will be reinforced at frequencies where the phase shift is near 0, and cancelled at frequencies where the phase shift is near 180 degrees. Since our example uses a single network, there will be no complete cancellation. To produce the phasing effect, several such networks are connected in series, and their phase shifts added. This gives rise to such advertising claims as "over 1200 degrees of phase shift!" which is true, impressive, and probably irrelevant. The other requisite for phasing is some method for varying the time constant of the networks over a wide range. In the example shown, varying R over a 400:1 range varies the cancellation frequency over the same amount, causing the phasing to shift from beyond audibility to the mid-bass region. As an added plus, during the period that R is changing, a frequency shift similar to doppler shift is created. This applies to the output of the all-pass network whether or not it is added to the input. Thus it is possible to generate a deep vibrato with no extra circuitry.

The frequency response of 8 all-pass networks is shown graphically for several values of R. The graphs are plotted on identical axes. Since the horizontal axis is logarithmic, the relative spacing of the nulls remains constant, although the absolute spacing in number of Hertz varies as R varies. In observing the graphs, note the following characteristics:

1. Below and above the ranges of the phase shift networks, the output of the system asymptotically approaches 2X the input.

2. The frequency ratio of the nulls is not constant and not harmonically related.

3. The shape of the nulls is sharp, the peaks rounded.

4. The total number of nulls is fixed and dependent upon the number of allpass networks.

5. At any time the nulls are clustered within one portion of the frequency spectrum.

#### FLANGING

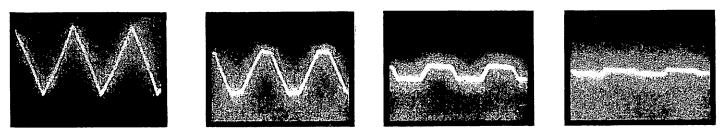

As we stated earlier, flanging is produced by mixing the output of two tape recorders, one of which is running a little slower than the other. Since the head-tohead distance is fixed, the transit time of the tape from the record head to the play head determines the path delay. Assume that the speed difference between tape machines is such that the differential delay between transit times is equal to 1 millisecond. Since one millisecond is the period of a 1kHz signal, it might be expected that a 1kHz input to the system would result in an additive signal, since the two outputs would add in-phase. On the other hand, a 500Hz input would have a 180 degree phase shift at 1 millisecond delay, and thus would completely cancel. Slightly less obvious is the fact that all signals at odd multiples of 500 Hz will undergo the same cancellation, since, for instance, the phase shift of 1500Hz is 360+180 degrees at 1 millisecond delay. Several graphs are presented showing the frequency response of a signal mixed with its delayed replica. Incidentally, all the graphs show the steady state response. We'll have a few words on transients later. In observing the graphs, note the following characteristics.

1. Below the first null, the output of the system asymptotically approaches 2X the input. There are always nulls at high frequencies.

2. The frequency ratio of the nulls is constant and harmonically related.

3. The shape of the nulls is uniform, and similar to the peaks.

4. The number of nulls increases as the delay increases.

5. At long delays, the entire frequency spectrum is substantially modified.

#### **COMPARISON**

The consequences of the differences in characteristics are striking. Intuitively,

one can feel that the flanging response should have more effect on the music, and in this case intuition is correct.

1. Because there are always nulls at high frequencies, the "jet plane" effect is more pronounced, even when the delay is fairly long.

2. Because the nulls are harmonically related, the effect on the tone of many instruments is more musically interesting. For instance: Assume an instrument is being played with a fundamental frequency of 440Hz. It will have harmonics at 880Hz, 1320Hz, 1760Hz, 2200Hz, etc. At a delay of 1.136 milliseconds, the fundamental and all odd harmonics will be cancelled out, leaving only the even harmonics. If the instrument shifts pitch, its entire tonality will change.

3. There's nothing much that can be said intuitively for advantages of sharp or rounded peaks, and since there's no simple way of comparing them subjectively, let's pass on this one.

4. The number of nulls increases as delay increases, and thus there is an overall broader effect on the input signal. It should be noted, however, that when the nulls are very closely spaced, the effect decreases since there is an averaging between the nulls and the peaks in psychoacoustic realms. As a practical matter, useful flanging occurs in the delay range of 50 microseconds to about 5 milliseconds, and devolves to a doubling effect after about 15 milliseconds.

5. Same comments as above.

The above comparisons refer only to the steady state behavior of the phasing/ flanging systems. In reality, two transient conditions occur (and interact). At issue are the subjective effects when:

1. Material is being phased or flanged while the time constant or delay of the network is being varied; and

2. The input is being changed while the constants of the network are held fixed.